SoC (Chip on System) һәм SiP (Пакеттагы Система) - заманча интеграль схемалар үсешендә мөһим этаплар, миниатюризация, эффективлык һәм электрон системаларны интеграцияләү мөмкинлеге бирә.

1. SoC һәм SiP төшенчәләре һәм төп төшенчәләре

SoC (Чиптагы система) - бөтен системаны бер чипка интеграцияләү

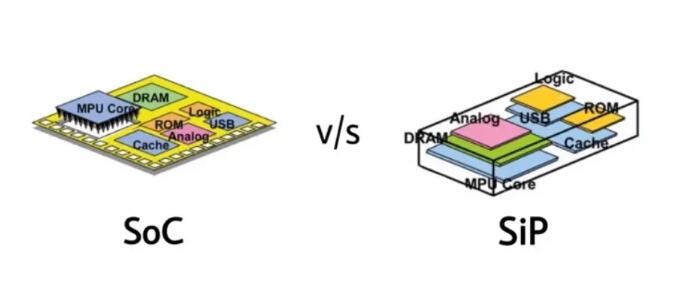

SoC күккә охшаган, анда барлык функциональ модульләр бер үк физик чипка эшләнгән һәм интеграцияләнгән. SoC-ның төп идеясы - электрон системаның барлык төп компонентларын, шул исәптән процессор (үзәк эшкәрткеч җайланма), хәтер, элемтә модуллары, аналог схемалар, сенсор интерфейслары һәм башка төрле функциональ модульләрне бер чипка берләштерү. SoC-ның өстенлекләре аның югары интеграция дәрәҗәсендә һәм кечкенә күләмендә, эштә, энергия куллануда, үлчәмнәрдә зур өстенлекләр бирә, аны югары җитештерүчән, энергиягә сизгер продуктлар өчен аеруча яраклы итә. Apple смартфоннарындагы процессорлар SoC чиплары үрнәге.

Мисал өчен, SoC шәһәрдәге "супер бина" га охшаган, анда барлык функцияләр дә эшләнгән, һәм төрле функциональ модульләр төрле катларга охшаган: кайберләре офис өлкәләре (процессорлар), кайберләре күңел ачу өлкәләре (хәтер), һәм кайберләре элемтә челтәре (элемтә интерфейсы), барысы да бер бинада (чип) тупланган. Бу бөтен системага бер кремний чипта эшләргә мөмкинлек бирә, югары эффективлыкка һәм җитештерүчәнлеккә ирешә.

SiP (Пакеттагы система) - Төрле фишкаларны берләштерү

SiP технологиясенә караш төрле. Бу бер үк физик пакет эчендә төрле функцияләр белән берничә чипны төрү кебек. Ул күп функциональ чипларны SoC кебек бер чипка интеграцияләү урынына, төрү технологиясе ярдәмендә берләштерә. SiP берничә чипка (процессорлар, хәтер, RF чиплары һ.б.) янәшә пакетларга яки бер үк модуль эчендә урнаштырырга мөмкинлек бирә, система дәрәҗәсендә чишелеш формалаштыра.

SiP төшенчәсен корал тартмасы җыю белән чагыштырып була. Корал тартмасы винтовка, чүкеч, бораулау кебек төрле коралларны үз эченә ала. Алар мөстәкыйль корал булса да, барысы да уңайлы куллану өчен бер тартмада берләштерелгән. Бу ысулның өстенлеге шунда: һәр корал аерым эшләнергә һәм җитештерелергә мөмкин, һәм алар сыгылучанлык һәм тизлекне тәэмин итеп, кирәк булганда система пакетына "җыелырга" мөмкин.

2. Техник характеристика һәм SoC һәм SiP арасындагы аермалар

Интеграция ысулы аермалары:

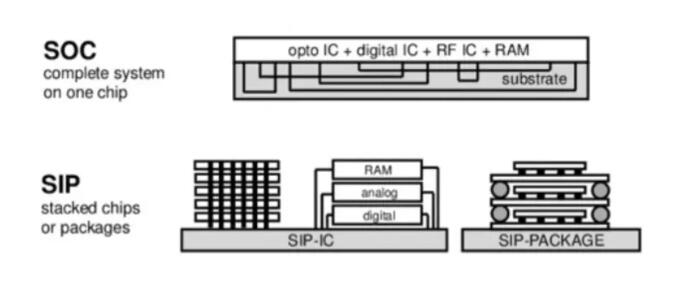

SoC: Төрле функциональ модульләр (үзәк эшкәрткеч җайланма, хәтер, I / O һ.б.) бер үк кремний чипта турыдан-туры эшләнгән. Барлык модульләр дә бер үк төп процесс һәм дизайн логикасы белән уртаклашалар, интеграль система формалаштыралар.

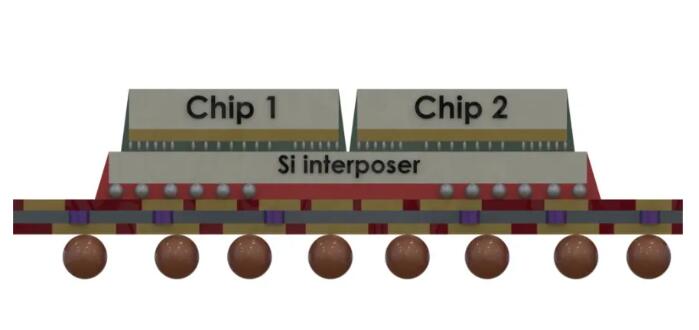

SiP: Төрле функциональ чиплар төрле процесслар ярдәмендә җитештерелергә мөмкин, аннары физик система формалаштыру өчен 3D упаковка технологиясе ярдәмендә бер упаковка модулында берләштерелергә мөмкин.

Дизайн катлаулылыгы һәм сыгылучылык:

SoC: Барлык модульләр дә бер чипка интеграцияләнгәнгә, дизайн катлаулылыгы бик югары, аеруча санлы, аналог, RF, хәтер кебек төрле модульләрнең уртак дизайны өчен. Моның өчен инженерлардан тирән домен дизайн мөмкинлекләре булырга тиеш. Моннан тыш, SoC'та теләсә нинди модуль белән дизайн проблемасы булса, бөтен чипны яңадан эшләргә кирәк булырга мөмкин, бу зур куркыныч тудыра.

SiP: Киресенчә, SiP зуррак дизайн сыгылмасы тәкъдим итә. Төрле функциональ модульләр системага салынганчы аерым эшләнергә һәм тикшерелергә мөмкин. Әгәр дә модуль белән проблема килеп чыкса, бүтән өлешләрне тәэсирсез калдырып, шул модулны гына алыштырырга кирәк. Бу шулай ук тизрәк үсеш тизлеген һәм SoC белән чагыштырганда түбән рискларга мөмкинлек бирә.

Процесс туры килү һәм проблемалар:

SoC: Санлы, аналог, RF кебек төрле функцияләрне бер чипка интеграцияләү процессның яраклашуында зур кыенлыклар белән очраша. Төрле функциональ модульләр төрле җитештерү процессларын таләп итә. мәсәлән, санлы схемаларга югары тизлекле, аз көчле процесслар кирәк, ә аналог схемалар төгәл көчәнеш белән идарә итүне таләп итә ала. Бер үк чиптагы бу төрле процесслар арасында яраклашуга ирешү бик авыр.

SiP: Пакетлау технологиясе ярдәмендә, SiP төрле процесслар ярдәмендә җитештерелгән чипларны берләштерә ала, SoC технологиясе алдында торган процессның яраклашу проблемаларын чишә ала. SiP берничә гетероген чипны бер пакетта бергә эшләргә мөмкинлек бирә, ләкин төрү технологиясенә төгәл таләпләр зур.

Тикшеренү циклы һәм чыгымнары:

SoC: SoC барлык модульләрне проектлау һәм тикшерүне таләп иткәнгә, дизайн циклы озынрак. Eachәр модуль катгый дизайн, тикшерү һәм сынау үтәргә тиеш, һәм гомуми үсеш процессы берничә ел дәвам итә ала, нәтиҗәдә зур чыгымнар. Ләкин, массакүләм җитештерүдә, югары интеграция аркасында берәмлек бәясе түбәнрәк.

SiP: R&P циклы SiP өчен кыскарак. SiP төрү өчен булган, расланган функциональ чипларны турыдан-туры кулланганга, ул модульне яңадан проектлау өчен кирәк булган вакытны кыскарта. Бу продуктны тизрәк эшләтеп җибәрергә мөмкинлек бирә һәм R&D чыгымнарын сизелерлек киметә.

Системаның эшләнеше һәм күләме:

SoC: Барлык модульләр дә бер үк чипта булганлыктан, элемтә тоткарланулары, энергия югалтулары, сигнал комачаулавы минимальләштерелә, бу SoC җитештерүчәнлегендә һәм энергия куллануда тиңсез өстенлек бирә. Аның зурлыгы минималь, аны смартфоннар һәм рәсем эшкәртү чиплары кебек югары җитештерүчәнлек һәм көч таләпләре булган кушымталар өчен аеруча яраклы итә.

SiP: SiP интеграция дәрәҗәсе SoC дәрәҗәсенә кадәр булмаса да, ул күп катламлы төрү технологиясе ярдәмендә төрле чипларны бергә туплый ала, нәтиҗәдә традицион күп чиплы чишелешләр белән чагыштырганда кечерәк зурлык. Моннан тыш, модульләр бер үк кремний чипка интеграцияләнү урынына физик яктан пакетланган булганлыктан, эш СоКныкына туры килмәсә дә, ул күпчелек кушымталар ихтыяҗларын канәгатьләндерә ала.

3. SoC һәм SiP өчен куллану сценарийлары

SoC өчен кушымта сценарийлары:

SoC гадәттә зурлыгы, энергия куллану, җитештерүчәнлеге өчен зур таләпләр булган кырлар өчен яраклы. Мәсәлән:

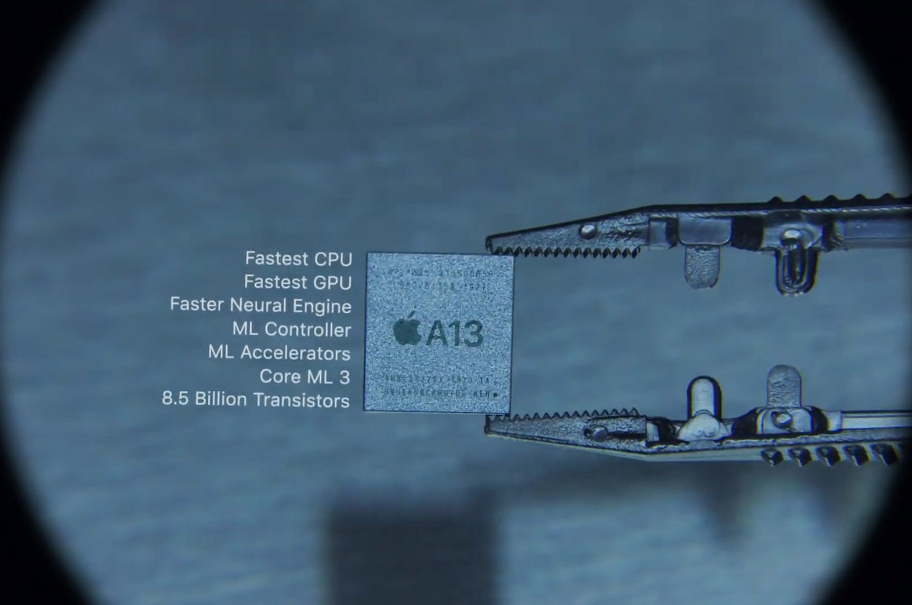

Смартфоннар: Смартфоннардагы процессорлар (мәсәлән, Apple-ның A серияле чиплары яки Qualcomm's Snapdragon кебек), гадәттә, үзәк эшкәрткеч җайланма, GPU, AI эшкәртү агрегатлары, элемтә модуллары һ.б.ны үз эченә алган югары интеграль СоКлар, көчле җитештерүчәнлекне дә, аз энергия куллануны да таләп итә.

Рәсем эшкәртү: Санлы фотоаппаратларда һәм дроннарда рәсем эшкәртү берәмлекләре еш көчле параллель эшкәртү мөмкинлекләрен һәм түбән тоткарлыкны таләп итәләр, алар SoC эффектив ирешә ала.

Perгары җитештерүчәнле урнаштырылган системалар: SoC аеруча IoT җайланмалары һәм кием әйберләре кебек каты энергия эффективлыгы таләпләре булган кечкенә җайланмалар өчен яраклы.

SiP өчен кушымта сценарийлары:

SiP куллану сценарийларының киң ассортиментына ия, тиз үсешне һәм күп функциональ интеграцияне таләп итә торган кырлар өчен яраклы:

Элемтә җиһазлары: база станцияләре, роутерлар һ.б. өчен, SiP продукт үсеш циклын тизләтеп, берничә RF һәм санлы сигнал процессорларын берләштерә ала.

Кулланучылар электроникасы: тиз яңарту циклына ия булган акыллы сәгатьләр һәм Bluetooth гарнитуралары кебек продуктлар өчен SiP технологиясе яңа функция продуктларын тизрәк эшләтеп җибәрергә мөмкинлек бирә.

Автомобиль электроникасы: Контроль модульләр һәм автомобиль системаларындагы радар системалары төрле функциональ модульләрне тиз интеграцияләү өчен SiP технологиясен куллана ала.

4. SoC һәм SiPның киләчәк үсеш тенденцияләре

СоК үсешенең тенденцияләре:

SoC югары интеграциягә һәм гетероген интеграциягә таба үсешен дәвам итәчәк, потенциаль AI процессорларын, 5G элемтә модулларын һәм башка функцияләрне интеграцияләүне үз эченә ала, акыллы җайланмаларның алга таба эволюциясенә этәрә.

SiP үсеш тенденцияләре:

SiP тиз арада үзгәрә торган базар таләпләрен канәгатьләндерү өчен, төрле процесслар һәм функцияләр белән чипларны тыгыз пакетлаштыру өчен, 2.5D һәм 3D упаковка кебек алдынгы төрү технологияләренә таяначак.

5. Йомгаклау

SoC күп функцияле супер бина төзүгә охшаган, барлык функциональ модульләрне бер дизайнда туплаган, эш башкару, зурлык, энергия куллану өчен бик югары таләпләр булган кушымталар өчен яраклы. SiP, киресенчә, системага төрле функциональ чипларны "төрү" кебек, сыгылучылыкка һәм тиз үсешкә күбрәк игътибар бирә, аеруча тиз яңартуны таләп итүче кулланучылар электроникасы өчен яраклы. Икесенең дә көчле яклары бар: SoC системаның оптималь эшенә һәм зурлыгын оптимизацияләүгә басым ясый, SiP системаның сыгылучылыгын һәм үсеш циклын оптимизацияләүгә басым ясый.

Пост вакыты: 28-2024 октябрь